2024-12-07 08:08:54

隨著人工智能(AI)、物聯(lián)網(wǎng)(IoT)、5G通信技術(shù)以及其他新興技術(shù)的快速發(fā)展,芯片設(shè)計(jì)領(lǐng)域正經(jīng)歷著前所未有的變革。這些技術(shù)對(duì)芯片的性能、功耗、尺寸和成本提出了新的要求,推動(dòng)設(shè)計(jì)師們不斷探索和創(chuàng)新。 在人工智能領(lǐng)域,AI芯片的設(shè)計(jì)需要特別關(guān)注并行處理能力和學(xué)習(xí)能力。設(shè)計(jì)師們正在探索新的神經(jīng)網(wǎng)絡(luò)處理器(NPU)架構(gòu),這些架構(gòu)能夠更高效地執(zhí)行深度學(xué)習(xí)算法。通過優(yōu)化數(shù)據(jù)流和計(jì)算流程,AI芯片能夠?qū)崿F(xiàn)更快的推理速度和更低的功耗。同時(shí),新材料如硅基光電材料和碳納米管也在被考慮用于提升芯片的性能。 物聯(lián)網(wǎng)設(shè)備則需要低功耗、高性能的芯片來支持其的應(yīng)用場(chǎng)景,如智能家居、工業(yè)自動(dòng)化和智慧城市。設(shè)計(jì)師們正在研究如何通過優(yōu)化電源管理、使用更高效的通信協(xié)議和集成傳感器來提升IoT芯片的性能和可靠性。此外,IoT芯片還需要具備良好的**性和隱私保護(hù)機(jī)制,以應(yīng)對(duì)日益復(fù)雜的網(wǎng)絡(luò)威脅。數(shù)字芯片作為重要組件,承擔(dān)著處理和運(yùn)算數(shù)字信號(hào)的關(guān)鍵任務(wù),在電子設(shè)備中不可或缺。北京MCU芯片后端設(shè)計(jì)

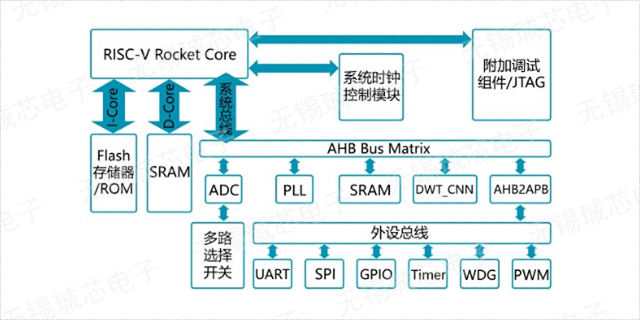

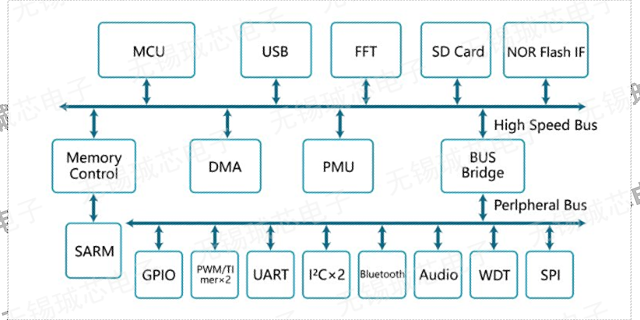

布局布線是將邏輯綜合后的電路映射到物理位置的過程,EDA工具通過自動(dòng)化的布局布線算法,可以高效地完成這一復(fù)雜的任務(wù)。這些算法考慮了電路的電氣特性、工藝規(guī)則和設(shè)計(jì)約束,以實(shí)現(xiàn)優(yōu)的布局和布線方案。 信號(hào)完整性分析是確保高速電路設(shè)計(jì)能夠可靠工作的重要環(huán)節(jié)。EDA工具通過模擬信號(hào)在傳輸過程中的衰減、反射和串?dāng)_等現(xiàn)象,幫助設(shè)計(jì)師評(píng)估和改善信號(hào)質(zhì)量,避免信號(hào)完整性問題。 除了上述功能,EDA工具還提供了其他輔助設(shè)計(jì)功能,如功耗分析、熱分析、電磁兼容性分析等。這些功能幫助設(shè)計(jì)師評(píng)估設(shè)計(jì)的性能,確保芯片在各種條件下都能穩(wěn)定工作。 隨著技術(shù)的發(fā)展,EDA工具也在不斷地進(jìn)化。新的算法、人工智能和機(jī)器學(xué)習(xí)技術(shù)的應(yīng)用,使得EDA工具更加智能化和自動(dòng)化。它們能夠提供更深層次的設(shè)計(jì)優(yōu)化建議,甚至能夠預(yù)測(cè)設(shè)計(jì)中可能出現(xiàn)的問題。廣東AI芯片工藝芯片架構(gòu)設(shè)計(jì)決定了芯片的基本功能模塊及其交互方式,對(duì)整體性能起關(guān)鍵作用。

在智慧城市的建設(shè)中,IoT芯片同樣發(fā)揮著關(guān)鍵作用。通過部署大量的傳感器和監(jiān)控設(shè)備,城市可以實(shí)現(xiàn)對(duì)交通流量、空氣質(zhì)量、能源消耗等關(guān)鍵指標(biāo)的實(shí)時(shí)監(jiān)控和分析。這些數(shù)據(jù)可以幫助城市管理者做出更明智的決策,優(yōu)化資源分配,提高城市運(yùn)行效率。 除了智能家居和智慧城市,IoT芯片還在工業(yè)自動(dòng)化、農(nóng)業(yè)監(jiān)測(cè)、健康**等多個(gè)領(lǐng)域發(fā)揮著重要作用。在工業(yè)自動(dòng)化中,IoT芯片可以用于實(shí)現(xiàn)設(shè)備的智能監(jiān)控和預(yù)測(cè)性維護(hù),提高生產(chǎn)效率和降低維護(hù)成本。在農(nóng)業(yè)監(jiān)測(cè)中,IoT芯片可以用于收集土壤濕度、溫度等數(shù)據(jù),指導(dǎo)灌溉和施肥。在健康**領(lǐng)域,IoT芯片可以用于開發(fā)可穿戴設(shè)備,實(shí)時(shí)監(jiān)測(cè)用戶的生理指標(biāo),提供健康管理建議。

芯片設(shè)計(jì)的申請(qǐng)不僅局限于單一**或地區(qū)。在全球化的市場(chǎng)環(huán)境中,設(shè)計(jì)師可能需要在多個(gè)**和地區(qū)申請(qǐng),以保護(hù)其全球市場(chǎng)的利益。這通常涉及到國際申請(qǐng)程序,如通過PCT(合作條約)途徑進(jìn)行申請(qǐng)。 除了保護(hù),設(shè)計(jì)師還需要關(guān)注其他形式的知識(shí)產(chǎn)權(quán)保護(hù),如商標(biāo)、版權(quán)和商業(yè)**。例如,芯片的架構(gòu)設(shè)計(jì)可能受到版權(quán)法的保護(hù),而芯片的生產(chǎn)工藝可能作為商業(yè)**進(jìn)行保護(hù)。 知識(shí)產(chǎn)權(quán)保護(hù)不是法律問題,它還涉及到企業(yè)的戰(zhàn)略規(guī)劃。企業(yè)需要制定明確的知識(shí)產(chǎn)權(quán)戰(zhàn)略,包括布局、許可策略和侵權(quán)應(yīng)對(duì)計(jì)劃,以大化其知識(shí)產(chǎn)權(quán)的價(jià)值。 總之,在芯片設(shè)計(jì)中,知識(shí)產(chǎn)權(quán)保護(hù)是確保設(shè)計(jì)創(chuàng)新性和市場(chǎng)競(jìng)爭力的重要手段。設(shè)計(jì)師需要與法律緊密合作,確保設(shè)計(jì)不侵犯他利,同時(shí)積極為自己的創(chuàng)新成果申請(qǐng)保護(hù)。通過有效的知識(shí)產(chǎn)權(quán)管理,企業(yè)可以在激烈的市場(chǎng)競(jìng)爭中保持地位,并實(shí)現(xiàn)長期的可持續(xù)發(fā)展。各大芯片行業(yè)協(xié)會(huì)制定的標(biāo)準(zhǔn)體系,保障了全球產(chǎn)業(yè)鏈的協(xié)作與產(chǎn)品互操作性。

在芯片設(shè)計(jì)領(lǐng)域,面積優(yōu)化關(guān)系到芯片的成本和可制造性。在硅片上,面積越小,單個(gè)硅片上可以制造的芯片數(shù)量越多,從而降低了單位成本。設(shè)計(jì)師們通過使用緊湊的電路設(shè)計(jì)、共享資源和模塊化設(shè)計(jì)等技術(shù),有效地減少了芯片的面積。 成本優(yōu)化不僅包括制造成本,還包括設(shè)計(jì)和驗(yàn)證成本。設(shè)計(jì)師們通過采用標(biāo)準(zhǔn)化的設(shè)計(jì)流程、重用IP核和自動(dòng)化設(shè)計(jì)工具來降低設(shè)計(jì)成本。同時(shí),通過優(yōu)化測(cè)試策略和提高良率來減少制造成本。 在所有這些優(yōu)化工作中,設(shè)計(jì)師們還需要考慮到設(shè)計(jì)的可測(cè)試性和可制造性。可測(cè)試性確保設(shè)計(jì)可以在生產(chǎn)過程中被有效地驗(yàn)證,而可制造性確保設(shè)計(jì)可以按照預(yù)期的方式在生產(chǎn)線上實(shí)現(xiàn)。 隨著技術(shù)的發(fā)展,新的優(yōu)化技術(shù)和方法不斷涌現(xiàn)。例如,機(jī)器學(xué)習(xí)和人工智能技術(shù)被用來預(yù)測(cè)設(shè)計(jì)的性能,優(yōu)化設(shè)計(jì)參數(shù),甚至自動(dòng)生成設(shè)計(jì)。這些技術(shù)的應(yīng)用進(jìn)一步提高了優(yōu)化的效率和效果。網(wǎng)絡(luò)芯片在云計(jì)算、數(shù)據(jù)中心等場(chǎng)景下,確保了海量數(shù)據(jù)流的實(shí)時(shí)交互與傳輸。廣東AI芯片

高效的芯片架構(gòu)設(shè)計(jì)可以平衡計(jì)算力、存儲(chǔ)和能耗,滿足多元化的市場(chǎng)需求。北京MCU芯片后端設(shè)計(jì)

工藝節(jié)點(diǎn)的選擇是芯片設(shè)計(jì)中一個(gè)至關(guān)重要的決策點(diǎn),它直接影響到芯片的性能、功耗、成本以及終的市場(chǎng)競(jìng)爭力。工藝節(jié)點(diǎn)指的是晶體管的尺寸,通常以納米為單位,它決定了晶體管的密度和芯片上可以集成的晶體管數(shù)量。隨著技術(shù)的進(jìn)步,工藝節(jié)點(diǎn)從微米級(jí)進(jìn)入到深亞微米甚至納米級(jí)別,例如從90納米、65納米、45納米、28納米、14納米、7納米到新的5納米甚至更小。 當(dāng)工藝節(jié)點(diǎn)不斷縮小時(shí),意味著在相同的芯片面積內(nèi)可以集成更多的晶體管,這不僅提升了芯片的計(jì)算能力,也使得芯片能夠執(zhí)行更復(fù)雜的任務(wù)。更高的晶體管集成度通常帶來更高的性能,因?yàn)楦嗟牟⑿刑幚砟芰透斓臄?shù)據(jù)處理速度。此外,較小的晶體管尺寸還可以減少電子在晶體管間傳輸?shù)木嚯x,從而降低功耗和提高能效比。 然而,工藝節(jié)點(diǎn)的縮小也帶來了一系列設(shè)計(jì)挑戰(zhàn)。隨著晶體管尺寸的減小,設(shè)計(jì)師必須面對(duì)量子效應(yīng)、漏電流增加、熱管理問題、以及制造過程中的變異性等問題。這些挑戰(zhàn)要求設(shè)計(jì)師采用新的材料、設(shè)計(jì)技術(shù)和制造工藝來克服。北京MCU芯片后端設(shè)計(jì)