2024-11-30 04:11:19

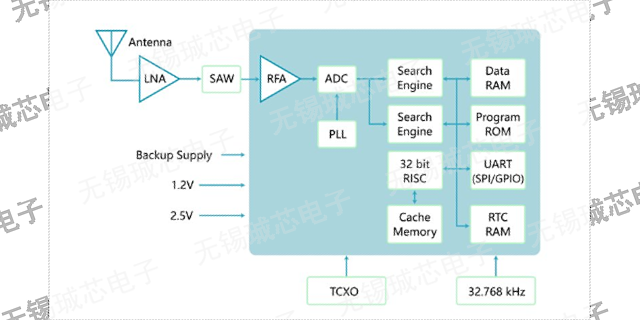

電子設計自動化(EDA)工具是現代芯片設計過程中的基石,它們為設計師提供了強大的自動化設計解決方案。這些工具覆蓋了從概念驗證到終產品實現的整個設計流程,極大地提高了設計工作的效率和準確性。 在芯片設計的早期階段,EDA工具提供了電路仿真功能,允許設計師在實際制造之前對電路的行為進行模擬和驗證。這種仿真包括直流分析、交流分析、瞬態分析等,確保電路設計在理論上的可行性和穩定性。 邏輯綜合是EDA工具的另一個關鍵功能,它將高級的硬件描述語言代碼轉換成門級或更低級別的電路實現。這一步驟對于優化電路的性能和面積至關重要,同時也可以為后續的物理設計階段提供準確的起點。網絡芯片作為數據傳輸中樞,為路由器、交換機等設備提供了高速、穩定的數據包處理能力。江蘇射頻芯片行業標準

芯片設計是一個高度專業化的領域,它要求從業人員不僅要有深厚的理論知識,還要具備豐富的實踐經驗和創新能力。隨著技術的不斷進步和市場需求的日益增長,對芯片設計專業人才的需求也在不斷增加。因此,教育機構和企業在人才培養方面扮演著至關重要的角色。 教育機構,如大學和職業技術學院,需要通過提供相關的課程和專業,培養學生在電子工程、計算機科學、材料科學等領域的基礎知識。同時,通過與企業的合作,教育機構可以為學生提供實習和實訓機會,讓他們在真實的工作環境中學習和應用理論知識。 企業在人才培養中也扮演著不可或缺的角色。通過設立研發中心、創新實驗室和培訓中心,企業可以為員工提供持續的學習和成長機會。企業還可以通過參與教育項目,如產學研合作,提供指導和資源,幫助學生更好地理解行業需求和挑戰。北京射頻芯片工藝精細化的芯片數字木塊物理布局,旨在限度地提升芯片的性能表現和可靠性。

芯片設計的申請不僅局限于單一**或地區。在全球化的市場環境中,設計師可能需要在多個**和地區申請,以保護其全球市場的利益。這通常涉及到國際申請程序,如通過PCT(合作條約)途徑進行申請。 除了保護,設計師還需要關注其他形式的知識產權保護,如商標、版權和商業**。例如,芯片的架構設計可能受到版權法的保護,而芯片的生產工藝可能作為商業**進行保護。 知識產權保護不是法律問題,它還涉及到企業的戰略規劃。企業需要制定明確的知識產權戰略,包括布局、許可策略和侵權應對計劃,以大化其知識產權的價值。 總之,在芯片設計中,知識產權保護是確保設計創新性和市場競爭力的重要手段。設計師需要與法律緊密合作,確保設計不侵犯他利,同時積極為自己的創新成果申請保護。通過有效的知識產權管理,企業可以在激烈的市場競爭中保持地位,并實現長期的可持續發展。

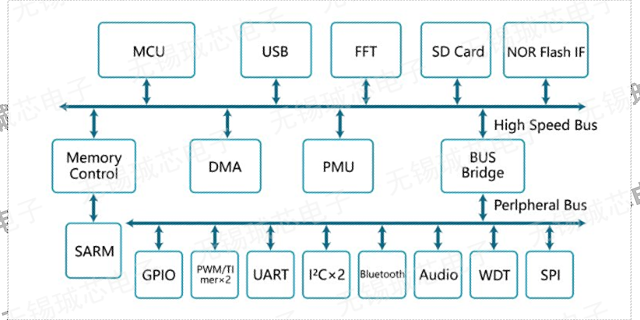

全球化的芯片設計也面臨著挑戰。設計師需要適應不同**和地區的商業環境、法律法規以及文化差異。此外,全球供應鏈的管理和協調也是一項復雜任務,需要精心策劃以確保設計和生產過程的順暢。 為了克服這些挑戰,設計師們需要具備強大的項目管理能力、跨文化溝通技巧和靈活的適應能力。同時,企業也需要建立有效的協作平臺和流程,以支持全球團隊的協同工作。 隨著技術的不斷進步和全球化程度的加深,芯片設計的國際合作將變得更加緊密。設計師們將繼續攜手合作,共同應對設計挑戰,推動芯片技術的創新和發展,為全球市場帶來更高效、更智能、更環保的芯片產品。通過這種全球性的合作,芯片設計領域的未來將充滿無限可能。 MCU芯片,即微控制器單元,集成了CPU、存儲器和多種外設接口,廣泛應用于嵌入式系統。

芯片技術作為信息技術發展的重要驅動力,正迎來前所未有的發展機遇。預計在未來,芯片技術將朝著更高的集成度、更低的功耗和更強的性能方向發展。這一趨勢的實現,將依賴于持續的技術創新和工藝改進。隨著晶體管尺寸的不斷縮小,芯片上的晶體管數量將大幅增加,從而實現更高的計算能力和更復雜的功能集成。 同時,為了應對日益增長的能耗問題,芯片制造商正在探索新的材料和工藝,以降低功耗。例如,采用新型半導體材料如硅鍺(SiGe)和鎵砷化物(GaAs),可以提高晶體管的開關速度,同時降低功耗。此外,新型的絕緣體上硅(SOI)技術,通過減少晶體管間的寄生電容,也有助于降低功耗。各大芯片行業協會制定的標準體系,保障了全球產業鏈的協作與產品互操作性。上海數字芯片行業標準

芯片前端設計完成后,進入后端設計階段,重點在于如何把設計“畫”到硅片上。江蘇射頻芯片行業標準

工藝節點的選擇是芯片設計中一個至關重要的決策點,它直接影響到芯片的性能、功耗、成本以及終的市場競爭力。工藝節點指的是晶體管的尺寸,通常以納米為單位,它決定了晶體管的密度和芯片上可以集成的晶體管數量。隨著技術的進步,工藝節點從微米級進入到深亞微米甚至納米級別,例如從90納米、65納米、45納米、28納米、14納米、7納米到新的5納米甚至更小。 當工藝節點不斷縮小時,意味著在相同的芯片面積內可以集成更多的晶體管,這不僅提升了芯片的計算能力,也使得芯片能夠執行更復雜的任務。更高的晶體管集成度通常帶來更高的性能,因為更多的并行處理能力和更快的數據處理速度。此外,較小的晶體管尺寸還可以減少電子在晶體管間傳輸的距離,從而降低功耗和提高能效比。 然而,工藝節點的縮小也帶來了一系列設計挑戰。隨著晶體管尺寸的減小,設計師必須面對量子效應、漏電流增加、熱管理問題、以及制造過程中的變異性等問題。這些挑戰要求設計師采用新的材料、設計技術和制造工藝來克服。江蘇射頻芯片行業標準